# A SXGA 3D Display Processor with Reduced Rendering Data and Enhanced Precision

Seok-Hoon Kim KAIST, Daejeon, Republic of Korea

#### I. INTRODUCTION

Recently, there has been tremendous progress in 3D graphics hardware for various multimedia devices such as mobile phones, portable multimedia players, and game consoles. Architecture evolution from a fixed pipeline to a programmable hardware makes it possible to render more realistic objects and describes various 3D effects. Enhanced computing power supports high-end interactive 3D graphics applications such as 3D games and GUI. However, no matter how the scenes of 3D graphics are vivid and photorealistic, they are displayed on a 2D display. Due to the lack of depth-perception of 2D displays and insufficient computing power of 3D graphics hardware, true reality is still not being provided to users.

On the other hand, a 3D display, a next generation display, provides depth perception by using stereoscopy [1] which shows realistic 3D effects to viewers. For example, when we watch an eye-max movie, we feel the objects floating and moving in the air. Owing to these realities, 3D displays are more and more used in various fields like military, medical, mobile, movies and monitor. However, current 3D displays cannot support interactive applications only to visualize preprocessed static pictures and video data because the image synthesis process for a 3D display requires to render many images and consumes much time to mix all rendered images.

In the previous work [2], we presented an SXGA (1280x1024) 3D display processor embedding a programmable 3D graphics rendering engine, which combined two distinguished regions, 3D graphics and 3D display, bringing synergetic coupling effects such as supporting both true realism and interactive applications at the same time. The previous work synthesizes 3D images from two view-images and a disparity-map [3] through view-interpolation process [4] and multiplexing process [5, 6]. Although the previous work has excellent performance to synthesize 3D images in real-time, it has high precision error through the multiplexing process, which lowers the quality of synthesized 3D images. In addition, the 3D graphics rendering engine in the previous work renders the same scene in two passes to generate the two view-images, which increases rendering time and requires much memory.

In this paper, we present a real-time 3D display processor with precision-enhanced multiplexing method and lower rendering amounts, which improves the quality of synthesized 3D images while conserving the interactive synthesis rate. Moreover, it reduces rendering time and required memory for source view-images, since it renders only one view-image and a few occluded data instead of two view-images.

#### II. RELATED WORK

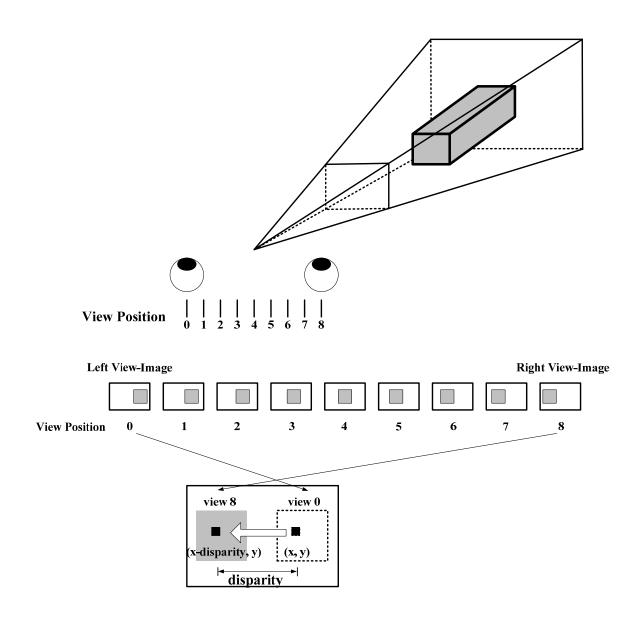

# A. The Amount of Rendering Works

An autostereoscopic display, a most popular 3D display, shows 3D images by allocating sub-pixels of different multiple view-images on the 3D LCD. Hence, multiple view-images are previously prepared for synthesizing 3D images. Since it is very large overhead to render all the view-images, view-interpolation algorithm was presented in [4]. To reduce the rendering overhead, most 3D image synthesis processes [7, 8] widely use view-interpolation algorithm. The view-interpolation process generates intermediate view-images for in-between view-positions from a left view-image, a right view-image and a disparity-map using spatial coherency between view-images as shown in Fig. 1. In the previous 3D display processor [2], a 3D graphics rendering engine renders the same scene twice to generate the left view-image and the right view-image. A depth-map is intrinsically produced through the rendering process, and it is linearly converted to a disparity-map by some equation. Since two view-images are taken from the same scene at different two view-positions, a leftmost view-position and a rightmost view-position, a 3D graphics rendering engine wastes its resources and rendering time to render duplicate data. It also requires additional memory and bandwidth to store and to load the needless data. The proposed method renders the scene only once and completely removes the duplicate data.

## B. Multiplexing Process

In multiplexing process, the sub-pixels of all view-images are allocated to the sub-pixel arrays of a 3D display. Each sub-pixel position of the 3D display has a view-number from zero to nine, which is evaluated by linear mapping equation. Then, a sub-pixel of some view-image which has its own view-position from zero to nine is mapping to matching positions whose evaluated view-numbers are equal to the view-position. Since the

evaluated value is floating-point while the view-position is integer, conventional multiplexing process [5, 6, 7, 8] must be executed after finishing the view-interpolation process in order to blend the sub-pixels of different view-images for fitting to the evaluated floating-point view-numbers. However, the conventional multiplexing process requires large external memory to store all the view-images, which causes frequent external memory accesses resulting in performance decrement.

On the other hand, the previous 3D display processor [2] reduces the frequent external memory accesses to 26.7% by using forward mapping method. It simultaneously executes the view-interpolation process and the multiplexing process without any temporal external memory for storing the results of the view-interpolation process. Although it increases synthesis rate to interactive rate, it has high precision error due to integer mapping.

Since both reverse multiplexing method and forward multiplexing method have critical disadvantages, we need enhanced multiplexing method which supports both interactive synthesis rate and high quality of synthesized 3D images.

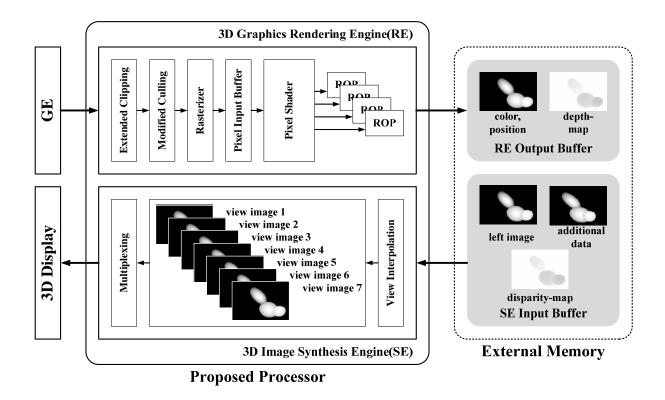

#### III. OVERVIEW

Fig. 2 shows the block diagram of the proposed 3D display processor which is based on the 3D graphics and 3D display merged architecture [2] to provide synergetic coupling effects such as freely inserting 3D effects to synthesized 3D images and directly using the outputs of a 3D graphics rendering engine. Since the previous 3D display processor has two critical weaknesses told in section II, rendering needless duplicate data and the integer multiplexing process with high precision error, we propose the architecture which removes those weaknesses.

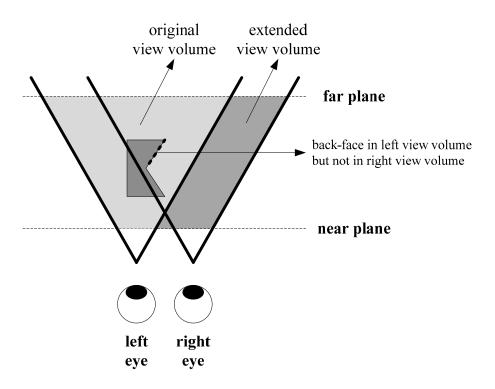

#### A. Effective 3D Graphics Rendering Engine

In the previous 3D display processor, the source data of the view-interpolation process, a left view-image and a right view-image, are rendered in two passes, which requires additional rendering time, memory and bandwidth for duplicate data. The proposed method renders only one view-image and a few occluded data instead of two view-images through only one rendering pass not two passes. To implement the proposed 3D graphics rendering engine, we modify two parts of a 3D graphics pipeline; clipping and back-face culling. The proposed method

extends the view volume including a right view volume as well as a left view volume, so that the pixels which are not in the left view volume but in the right view volume are not clipped as shown in Fig. 3. Similarly, in back-face culling, some pixels are not back-face in the right view-position but back-face in the right view-position. We must not cull these pixels and stores them in additional frame buffer. Although the proposed clipping and culling method increases operations for clipping and back-face culling, it renders the same models only once and completely removes duplicate data, while the previous method renders the same things twice. Therefore, the proposed method enormously reduces total rendering operations, rendering time and frame buffer size compared to the previous 3D display processor.

#### B. 3D Display Image Synthesis Engine with Enhanced Multiplexing

Conventional multiplexing process blends sub-pixels of different view-images and allocates them to proper positions of sub-pixel arrays of a 3D display. Since it stores all view-images in external memory, it cannot synthesize 3D images in real-time due to frequent external memory accesses. On the other hand, the previous work executes integer mapping without storing any temporal data, which increase synthesis rate to interactive rate but causes precision errors about 25% compared to ideal multiplexing. We propose enhanced multiplexing method which reduces precision errors while conserving interactive synthesis rate. To synthesize 3D images in real-time, we design the proposed architecture based on the previous work and modify two parts; increasing the precision of view-numbers and adding two flag bits per a sub-pixel of a 3D display. We round off the view-numbers to two decimal place so that the view errors are reduced to less than 1%. Then, the evaluated values are divided into integer part and fragment part. We find proper position to be filled with the integer part and blend the color to be mapped by multiplying the fragment part. Then, we check the filled positions with flag bits to avoid overlapping cases. Although the proposed method increases the view-number evaluator by 5bits and requires additional flag bits, it reduces the precision errors under 1% while conserving the interactive synthesis rate.

## References

- [1] D. Scharstein, "View Synthesis Using Stereo Vision," volume 1583 of LNCS. Springer-Verlag, 1999.

- [2] Seok-Hoon Kim, et al., "A 36fps SXGA 3D Display Processor with a Programmable 3D Graphics Rendering Engine," IEEE International Solid-State Circuit Conference, 2007, pp.276-277, Feb., 2007

- [3] Goshtasby, "A Stereo Correspondence by Selective Search," Proc. Japan Computer Vision Conf., 1-10, July, 1989.

- [4] E. Chen, et al., "View Interpolation for Image Synthesis," SIGGRAPH, pp.279-288, Aug., 1993.

- [5] C. Van Berkel, "Image preparation for 3D-LCD," Proc. SPIE Stereoscopic Displays Virtual Reality Systems, Vol.3639, pp.84-91, May, 1999.

- [6] Yun-Gu Lee, et al., "Reduction of the distortion due to non-ideal lens alignment in lenticular 3D displays," Proceedings of SPIE Stereoscopic Displays and Virtual Reality System 2005, vol. 5664, pp. 506-516, Jan., 2005.

- [7] Balasubramanian, K., "On the realization of constraint-free stereo television," IEEE Transactions on Consumer Electronics, pp895-902,

- [8] Konrad. J, Agniel. P, "Subsampling models and anti-alias filters for 3-D automultiscopic displays," IEEE Transactions on Image Processing, Jan., 2006

# List of Figures

Figure 1 View-interpolation Algorithm

Figure 2 Total Architecture of Proposed Processor

Figure 3 Extended View Volume and Back-face

Figure 1 View-interpolation Algorithm

Figure 2 Total architecture of Proposed Processor

Figure 3 Extended View Volume and Back-face